Оборудование сетевых коммутаторов

Одно из отличий недорогих коммутаторов Ethernet от более дорогих – в степени внутреннего параллелизма вычислений, который они могут поддерживать. Например, если пакеты приходят на входные порты 1, 2 и 3 и они должны быть выведены на выходные порты соответственно 4, 5 и 6, и если коммутатор может передать их одновременно, это означает, что он может «расправляться» с пакетами с такой же скоростью, с какой они прибывают на вход коммутатора. Самый трудный случай для коммутатора с 2N портами – когда пакеты непрерывно прибывают на N входных портов и убывают с N выходных портов. Это означает, что за время, требуемое на передачу одного пакета, коммутатор передаёт N пакетов параллельно.

Иногда такая скорость бывает избыточной. Если вся нагрузка на коммутатор заключается в приёме и передаче последовательно поступающих пакетов на один порт, например, когда он подключён к серверу или к Интернет, то такая производительность в N раз лучше, чем требуется. Конечно, на выходе при этом может образовываться очередь из обработанных пакетов, однако, это не означает недостаточной производительности самого коммутатора. Поэтому, чем больший параллелизм вычислений может поддерживать коммутатор, тем лучше.

Самая простая архитектура коммутатора, когда он не очень отличается от «стандартного» компьютера, это модель с общей памятью (shared-memory model). Такая система состоит из одного процессора (CPU), одного массива общей памяти и периферийных шин, и нескольких интерфейсов Ethernet. Когда на входной порт прибывает пакет, то CPU копирует пакет со входного интерфейса в оперативную память (RAM), определяет, куда его нужно направить, и затем копирует пакет на выходной интерфейс. Чтобы работать со скоростью передачи пакетов 100 Мбит/с, скорость внутренней передачи должна быть по крайней мере 200 Мбит/с. Максимальная скорость такого устройства зависит в основной от скорости передачи шины от портов в RAM (т.н. называемая шина front-side bus). Шина USB 3.0 может работать со скоростью 5 Гбит/с. При скорости Ethernet в 100 Мбит/с, такая шина теоретически может передать (5Гбит/с)/(200Мбит/с) = 25 пакетов за время, требуемое для прибытия одного пакета на вход, с поддержкой до 50 портов на коммутаторе. Однако, если скорость в сети Ethernet – 1 Гбит/с, то может быть принято только два пакета за время считывания одного пакета со входного порта. Для обычных коммутаторов с пятью портами ввода-вывода этого достаточно, и такие коммутаторы могут поддерживают такую степен параллелизма. Но сейчас скорости Ethernet составляют 10G или даже 40G, при 24-портовых коммутаторах, что в дата-центрах не редкость. Поэтому архитектура shared-memory не может быть признана подходящей для высокопроизводительных коммутаторов.

Когда требуется более высокая степень параллелизма, применяются другие архитектуры, которые называются switch fabrics (многовходовая коммутационная матрица). Это сеть из NхN коммутационных узлов, которые могут переключаться под управлением процессора коммутатора. Такая коммутационная матрица позволяет производить одновременные параллельные соединения между N входами и N выходами.

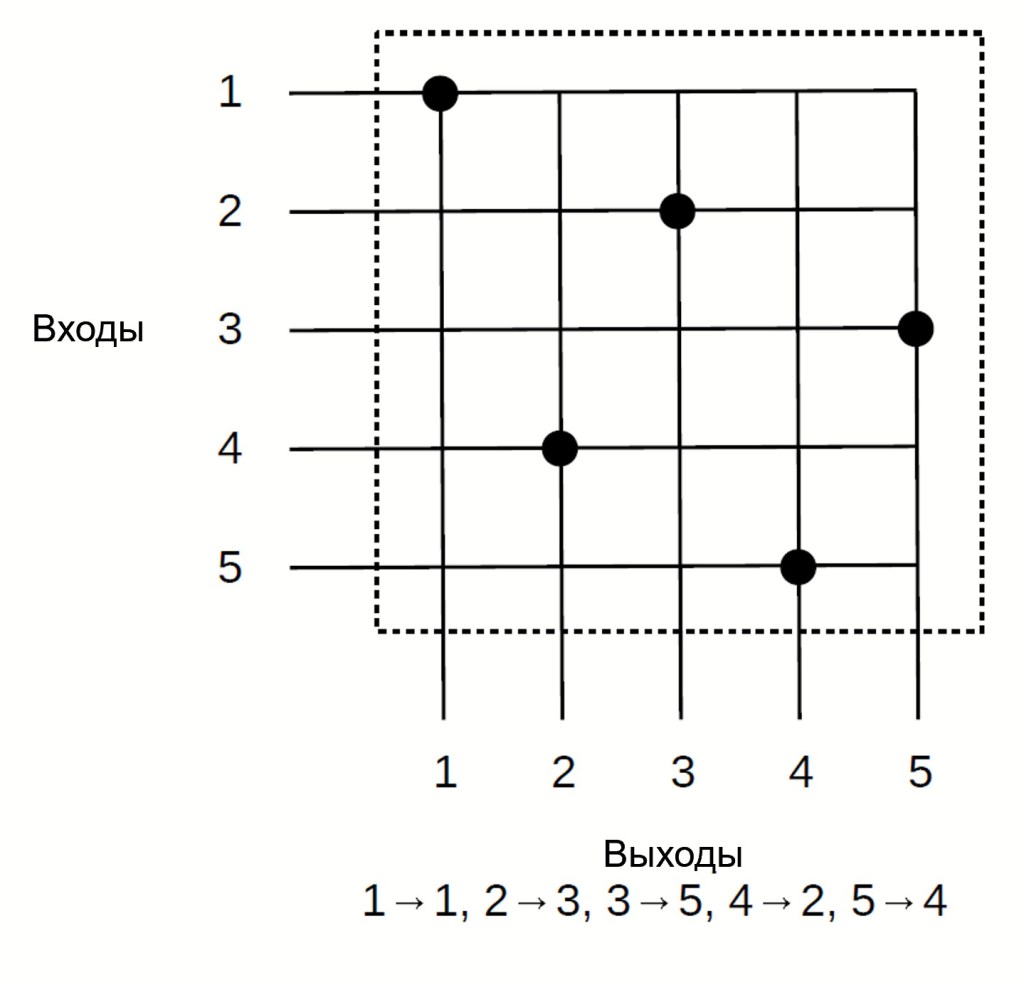

На рисунке показана коммутационная матрица 5х5, с 5 входами и 5 выходами. В сети Ethernet любой порт может быть как входным, так и выходным, но это не имеет большого значения. Показаны пять параллельных соединений, со входов 1-5 на выходы 1, 3, 5, 2 и 4 соответственно. Точками показаны узлы коммутации (ключи) в замкнутом состоянии. Пакеты передаются последовательно через каждое соединение матрицы. Понятно, что если пакеты будут прибывать на входной порт быстрее, чем они будут передаваться с выходного порта, то они должны помещаться в очередь на выходном порте. Однако, если на один выходной порт должны передаться пакеты с нескольких входов, то они также должны на короткое время помещаться в очередь на этом порте.

Подобные матрицы, с различными вариациями, используются при построении высокоскоростных Ethernet-коммутаторов.

Другой технологией построения высокопроизводительных коммутаторов является CAM (Content-Addressable Memory), которая позволяет производить поиск в таблице передачи пакетов (forwarding table) в течение одной загрузки в память. В коммутаторе с общей памятью (shared-memory) поиск каждого адреса назначения пакета должен производиться в хэш-таблице, или другой структуре данных, включая вычисление значения хэша[1] (hash value), и этот процесс может быть на порядки длительнее, чем однократная загрузка в оперативную память.

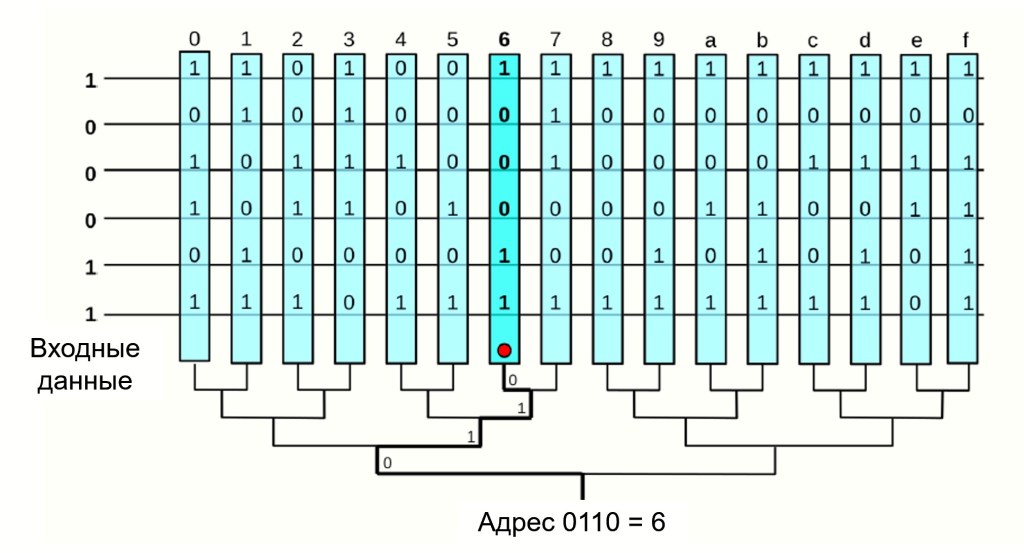

У некоторых коммутаторов таблица forwarding table часто называется таблицей CAM. Память CAM состоит из большого числа N регистров памяти, которые подключены к общей шине ввода данных. Для Ethernet-коммутации, ширина слова адресуемых данных на шине и регистрах должна быть по меньше мере 48 бит. При активации входной шины, каждый регистр памяти сравнивает значение на шине со своим собственным значением. Если эти значения совпадают, то регистр включает свою входную линию.

Схема двоичного кодирования затем конвертирует число k<N этого регистра в двоичное значение, представляющее адрес регистра k. Регистр разрешает связи, выбирая например, число первого регистра для сравнения.

На рисунке, разрядность слова данных равна 6, и есть 16 регистров пронумерованных от 0 до F в шестнадцатеричной системе. В регистре 6 записано число 100011, соответствующее входным данным. Выходное слово схемы кодирования является соответствующим адресом 0110.

Распространённый вариант CAM – троичная схема TCAM (Ternary CAM) в которой, кроме двоичных состояний 0 и 1 имеется третий символ «подстановочного знака» (wildcard), который обращает в 0 любую двоичную цифру, попавшую в разряд wildcard. В TCAM каждый регистр памяти имеет пару соответствующего регистра «маски». Для любого заданного бита соответствие декларируется только если бит шины соответствует регистру бита, либо если соответствующий бит маски равен 0.

TCAM чаще всего используется для IP-адресов, а не Ethernet-адресов, когда цель состоит в том, чтобы получить соответствие только адресных битов, соответствующих префиксу сети. В этом случае содержание маски представляет собой маску IP-адреса подсети.

Более подробно методы адресации, такие как CIDR (Classless Internet Domain Routing), будут рассмотрены позднее.

[1] Хэш-функция (функция свёртки) — преобразование массива входных данных произвольной длины в выходную битовую строку фиксированной длины по определённому алгоритмом. Эта строка однозначно характеризует входной массив данных (хэширование).

Уведомление: Сетевые технологии (13). Virtual LAN (VLAN) | Telecom & IT

ПОЛЕЗНО!

НравитсяНравится